前几天,托尼在网站上闲逛的时候,注意到这样一条新闻。

全球最大的芯片代工巨头台积电,其高管力挺摩尔定律,认为这个定律没有消亡,仍然可以通过增加晶体管密度,实现计算性能的提高。

如果托尼没有记错的话,在摩尔定律是否已经失效这个话题上,这已经不是第一次有硅谷圈的大佬放话对它公开做出判断了。

前阵子唱衰说摩尔定律已经死了的人,还是大名鼎鼎的英伟达创始人兼首席执行官黄仁勋。

关于摩尔定律是否失效的争论由来已久,理工科的差友们,可能对摩尔定律也已经再熟悉不过。

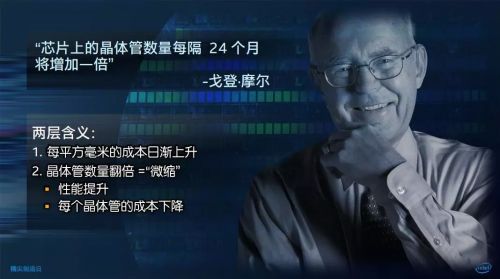

1965 年,作为后来英特尔公司联合创始人之一的戈登·摩尔,在当时老牌专业杂志《 Electronics 》上,发表了一篇主题为“ 让集成电路填满更多的元件 ”的评论性文章。

在文章中,戈登·摩尔根据前几年自己身处行业发展规律的观察,提出了一个对未来半导体行业发展的著名预测:

当价格不变时,单位面积芯片上可容纳的晶体管数量,约每隔 18-24 个月便会增加一倍,性能也将提升一倍。

这就是现在我们熟知的摩尔定律,也是我们平时说的电子产品早买早享受,晚买享优惠,不买免费送的最早来源所在。

从摩尔定律的历史产生背景我们不难知道,它不是天然存在的自然规律,也不是准确无误的物理法则,仅仅只是对于趋势的经验推测。

但就这么一个预测,却在后来奇迹般的指导了半导体产业整整五十多年的发展,甚至成为计算机行业进步背后的金科玉律,深刻影响着硬件产品的更新迭代。

无论是英特尔还是三星以及台积电,在半导体工艺的研发上,前几十年来一直都是依据摩尔定律的规律来设定的研发目标。

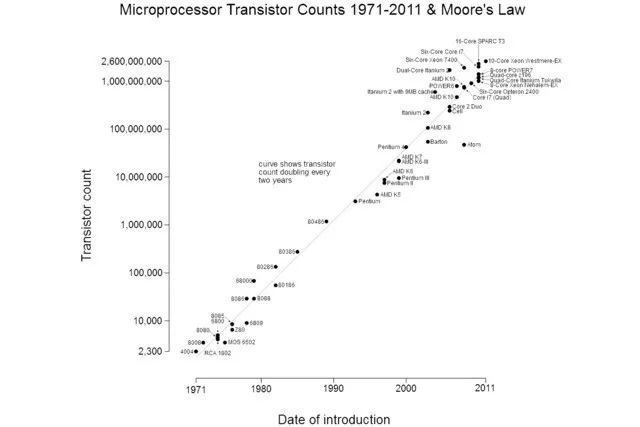

1971-2011 年台式电脑处理器的性能拟合摩尔定律

拿计算机上的 CPU 来说,从早年的 180nm 到后来的 130nm 再到 90、65、45、32、28 nm。。。

它的制程在逐年变小的同时,芯片上集成的晶体管数量越来越多,性能也越来越强,在这个过程中,一直遵循着摩尔定律推进。

这一规律带给我们最直观的感受就是,大概每隔两年左右,新发布的手机或者电脑等电子产品,性能会远比前代的产品高出不少。

Macbook Pro 新旧款运行软件速度对比

前几年还只能用来打电话发短信玩玩贪吃蛇和俄罗斯方块的手机,到如今已经能够用来拍视频看直播玩 AR 游戏了。

昔日旗舰不如狗,新品出来后,前代产品的价格往往也会跌得很多,甚至很快就被市场淘汰。

然而就在最近这几年,关于摩尔定律放缓或者失效的论调越来越多。

有人说,摩尔定律已经成为一个技术问题,还有人说遵循摩尔定律已经没有意义,更有人说,摩尔定律已死。

硅谷创业教父 Steve Blank“ 摩尔定律在十年前就失效了,只是人们没有察觉而已 ”

出现这些声音的原因,是因为按照摩尔定律的预测,随着时间的推移,芯片上所能集成的晶体管数量会越来越多,性能会以每两年左右翻一倍的速度增长,但事实并非如此。

我们都知道现在的电子计算机能做到的所有功能,本质上都是通过 0 ,1 组成的二进制数来进行存储和运算实现的。

早期计算机内部产生 0 和 1 电路逻辑的元器件是真空管,体积大发热严重的同时寿命还短,所以它很快就被体积更小也更稳定晶体管所取代。

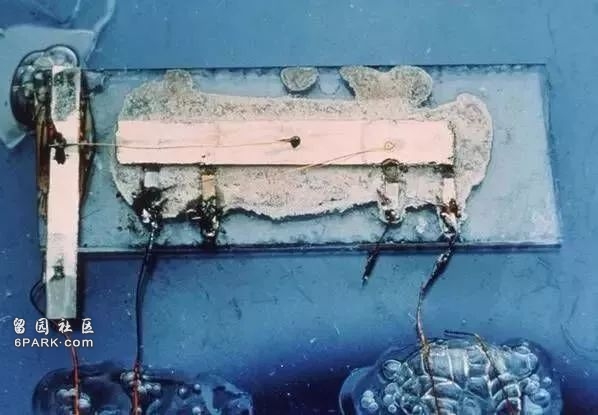

世界上第一只晶体管

晶体管就好比一个靠电压驱动的开关,工作原理就是把一端( 左边的 Source )的电子移动到另外一端( 右边的 Drain )。

其中这两端的间距( 红色区域的长度 ),代表的就是厂商们在芯片上所宣传的 XXnm 的制程数字,电子( 黄色的球 )在这两端移动时所经过的地方就叫做沟道( 红色区域 )。

这样一来晶体管内部的沟道导通电子流动时便可设为 1,沟道断开电子无法转移时则为 0,提供给计算机 0,1 逻辑的功能就这样实现了。

在摩尔定律刚提出的那会,晶体管的体积差不多就和一只 AirPods 耳机一样大,一块电路板上,最多也只有几个晶体管。

世界上第一块集成电路

在晶体管尺寸还比较大的情况下,这种单纯依靠缩小尺寸集成更多晶体管来提高性能确实可行,因为制程做小两端的间距变短了,电子在两端移动所用的时间变少,运行速度自然就更快。

如今随着半导体技术和集成电路的发展,晶体管的尺寸越来越小,在同样的面积下,已经能够容纳超过几十亿个晶体管。

苹果 7nm 工艺制程的 A12X 芯片拥有 100 亿个晶体管

对比 A12 性能几乎是翻倍

但如果想继续沿着摩尔定律的进程再进一步缩小晶体管的尺寸时,更艰难的问题也随之而来。

现在的晶体管制程已经小到了 10nm 和 7nm,当它的尺寸再缩小到 5nm、3nm 甚至 1nm 时,就有一个很严重的问题阻碍了现有的晶体管技术 —— 量子隧穿!

我们知道,在原子尺寸的领域里,经典物理学就已经失效了,人们必须要接受看起来非常玄乎的量子力学。。

而量子隧穿效应同样很违背人类的直觉。。

举个栗子,正常情况下,一个人不借助梯子是无法跨越5米的高墙的,无论这个墙怎么变薄,高度在那里摆着,没有工具的话,人就无法跨过去。

但是在量子领域,如果这个墙变的和人的厚度差不多的时候,人就有一定几率闪到墙对面去。。。

量子力学与宏观世界相悖

同样的,原本需要施加电压才能导通的晶体管,尺寸缩小到原子级别后,电子的位置就变成了概率出现,在没有通电的情况下也能发生转移,这就是量子隧穿效应。

效果和《 蚁人2 》里的幽灵穿墙差不多

这时候,因为晶体管提供 0,1 逻辑的准确率下降,造成的运算准确率也随之下降。

你无法确定薛定谔的猫是死是活你也无法无法预测电子出现的位置

不仅如此,晶体管尺寸越小,它的漏电现象也越严重,甚至线路之间离得太近也会导致寄生电容暴涨。。。

这些都是不能够用现有工艺严格控制的意外的产物。

所以讲到这里差友们可能就明白了。

严格以两年的时间晶体管数量增加一倍并且性能提升一倍的标准来说,即使晶体管尺寸能做到那么小,有那么多不可靠性,谁又敢用呢?

2015 年国际半导体技术发展路线图:摩尔定律五年内将失效

至于摩尔定律失效之后,是不是以后的电子产品性能提升会越来越慢甚至停滞不前?

那倒不一定,像原先一样靠堆更多的晶体管在芯片上面来提升性能的路子走不通了,还可以换条路走。

三星将在 2021 年实现的 3nm GAA 工艺

比如将晶体管的导电沟道换成石墨烯等更有利于电子迁移的材料,这样晶体管切换 0,1 的逻辑会变快,运行速度照样能提高。

或者重新设计新的晶体管架构,使它能够处理 0,1 逻辑功能变多,这样原先需要两个晶体管才能实现逻辑功能,现在只要一个晶体管,也同样能提高芯片的性能。

甚至改变栅极材料也是一种方法。。。

后摩尔时代的新技术突破方向

虽然这些新技术也有这样或者那样的门槛,但是,总是有解决的希望的。

台积电已经在推行 5 nm 了而英特尔还在 10 nm 苦苦挣扎。。。

摩尔定律从诞生到现在也已经过了五十四年,其实早在 20 多年前,就已经有人提到过定律终将失效,但在这些年里,对于它是否失效的争论从未停息。

与其说他们讨论的重点是在摩尔定律上,不如说他们是想借着摩尔定律来彰显自己的技术实力:

你看,我还有能力沿着摩尔定律继续走下去,怪你们自己太垃圾,所以跟不上。